1. SOP (Small Outline Package, 표면실장 2방향 L자형 패키지) (일본 JEITA(EIAJ)규격)

= SOIC (Small Outline Integrated Circuit) (미국 JEDEC규격)

< Pitch : 50MIL(1.27mm) / Pin : 8~44 >

< Typ.Pin counts : 24, 28, 32, 40, 44 >

- 표면실장의 대표적인 형태. QFP에 반해 2방향인 SOP는 회로의 규모가 크지 않을 때 사용한다.

- SOIC는 미국 JEDEC 규격에 따른 SOP의 다른 이름. 하지만 EIAJ 규격에 따른 SOP가 더 일반적이다.

(이 외에도, SOL(Fujitsu) 등 각각 다른 패키지 표준이 존재함에 따라, 교환 가능한 부품을 제시하기 힘든 모호한 패키지다.)

1-1. SSOP (Shrink SOP)

< Pitch : 1.0mm|0.8mm|0.65mm|0.5mm / Pin : 8~80 >

- 피치를 줄여 실장밀도를 높인 SOP.

- 실장 높이는 1.5mm~1.7mm정도로 TSOP, TSSOP에 비해 두껍다.

1-2. TSOP (Thin SOP)

TYPE1 : < Pitch : 0.6mm | 0.55mm | 0.5mm > < Typ.Pin counts : 28, 32, 40, 48, 56 >

TYPE2 : < Pitch : 50MIL(1.27mm) | 0.8mm | 0.65mm > < Typ.Pin counts : 20, 24, 26, 28, 32, 40, 44, 50, 54, 66 >

- 실장높이가 1.0mm 이하로 얇은 SOP.

- 리드가 짧은폭에서 나오느냐, 긴폭에서 나오느냐에 따라 TYPE1(짧은폭)과 TYPE2(긴폭)로 나뉜다. (일본 EIAJ규격)

- DRAM, SRAM과 플래시메모리 IC는 대개 BGA로 교체될때까지 TSOP 타입을 사용했다.

1-3. TSSOP (Thin & Shrink SOP)

- 좁은 피치(SSOP) + 1.0mm 이하로 얇은 실장높이(TSOP). < Pitch : 0.65mm | 0.5mm / Pin : 8~64 > (일본 T.I.JAPAN명명)

1-4. UTSOP (Ultra Thin SOP)

- 실장높이가 0.65mm 이하로 얇은 SOP. (일본 FUJITSU명명)

1-5. 패키지 크기 비교 : SOP > TSOP > SSOP > TSSOP > UTSOP

2. SON (Small Outline Non-leaded Package, 표면실장 2방향 패드형 패키지)

< Pitch : 1.0mm | 0.5mm >

- 점유 면적과 중량을 줄이기 위해 리드를 없앤 형태.

- 실장높이가 1mm 이하로 얇다.

- 패드형 특성상 기생 인덕턴스가 적어 고속, 고주파 동작에 적합하다.

- 직선형/J자형 패키지에 비해 리드 평탄도 문제가 발생하지 않는다.

표면실장 패키지 (4방향)

1. QFP (Quad Flat (L-leaded) Package, 표면실장 4방향 직선형/L자형 패키지)

< Pitch : 0.4mm | 0.5mm | 0.65mm | 0.8mm | 1.0mm / Pin : 32~304 >

< Typ.Pin counts : 44, 56, 64, 80, 100, 128, 160, 208, 240, 272, 304 >

- 표면실장의 대표적인 형태.

- 1970년대부터 일본 가전제품에 사용되었으며, 90년대 초부터 유럽/미국에서 표준화되었다.

- 핀 번호는 점으로부터 반시계 방향으로 돈다.

1-1. TQFP (Thin QFP)

- 실장높이가 1.0mm~1.4mm로 얇은 QFP. < Pitch : 0.4mm | 0.5mm >

- TQFP와 LQFP의 분류기준은 모호하여, 같은 사이즈와 피치간격이라 할지라도 서로 다르게 분류하는 경우가 많다.

- 여하튼 ATmega328p-AU는 Atmel에 의하여 TQFP로 분류된다.

1-2. LQFP (Low-profile QFP ) :

- 실장 높이가 1.4mm로 얇은 QFP. < Pitch : 0.4mm | 0.5mm | 0.65mm | 0.8mm >

1-3. PQFP (Plastic QFP)

- 실장높이는 2.0mm~3.8mm. 플라스틱으로 패키지가 제작된다.

1-4. CQFP (Ceramic QFP)

- 세라믹으로 패키지가 제작된다. Motorola 사에 의해서만 사용되었다.

1-5. MQFP (Metric AFP)

- 인치가 아닌, 미터법으로 피치간격이 할당된 QFP.

2. QFN (Quad Flat Non-leaded Package, 표면실장 4방향 패드형 패키지)

= MLF/MLP (Micro Lead Frame Package)

< Pitch : 40MIL(1.016mm) | 50MIL(1.27mm) >

- 점유 면적과 중량을 줄이기 위해 리드를 없앤 형태.

- 실장높이가 1mm 이하로 얇다.

- 직선형/J자형 패키지에 비해 리드 평탄도 문제가 발생하지 않는다.

- ATmega 시리즈를 비롯하여, 정말 많이 쓰이고 있다.

- 패드형 특성상 기생 인덕턴스가 적어 고속, 고주파 동작에 적합하다.

(Air-Cavity를 적용하지 않은 QFN 패키지는 플라스틱으로 제조 가능하며, 일반적으로 최대 2-3GHz의 어플리케이션에 제한된다.)

(Air-Cavity가 적용된 QFN 패키지는 20-25GHz의 어플리케이션에 사용될 수 있다.)

- 지속적인 열 사이클링에 인한 기계적 피로에 약하여, 높은 신뢰성이 필요한 자동차/항공보다, 소비자 가전에 주로 적용된다.

(-40'C~125'C의 지속적인 열 사이클링에서 10,000회 이상 견딜 수 있는 QFP에 반해, QFN은 1,000~ 3,000회에서 오류를 발생한다.)

(이에 대한 보완책으로 일반적은 QFN, MLF는 솔더링 가능한 열 패드를 갖는다.)

2-1. TQFN (Thin QFN)

< Pitch : 0.40mm | 0.50mm | 0.65mm >

- 0.8mm의 얇은 두께와, 보다 더 좁은 피치간격을 가진 QFN 패키지.

표면실장 패키지 (매트릭스)

0. 표면실장 패키지 (매트릭스)

- 타 표면실장 패키지에 비해, 피치 간격이 좁아질수록 발생할 인접한 핀과의 결합 리스크 부담이 적다.

- 별로 알고싶지도 않을 만큼 고난이도의 정밀한 실장기술이 필요하며, 납땜 후 납땜결합을 찾기 힘들다.

(X선, CT스캐닝기계, 내시경 등이 사용되거나, 혹은 JTAG를 통한 바운더리 스캐닝이 사용된다.)

(아니면 땜질 후 염료에 통채로 담궜다가 건조시킨뒤 패키지를 제거하고 솔더위치에 염료가 묻어있는지 검사하는 방법도 있다고..)

- 보수가 어려워, 영구적으로 장착한다는 가정 하에 사용한다.

- 소켓 장착에 적합하지 않다.

- QFP등의 패키지와 비교하여 실장불량률이 적고, 핀 수에 대해 자유롭다.

1. BGA (Ball Grid Array, 표면실장 매트릭스 볼형 패키지)

(환공포증생기겠네 시바꺼)

- 패키지 밑면의 볼을 매트릭스로 나열한 형태이다.

- 기존 패키지보다 기생 인덕턴스가 적다.

- ATmega640, ATmega1280, ATmega2560 등에서 CBGA(Ceramic BGA)타입 패키지가 제공되고 있다. (우측사진)

- 현재 고성능 CPU의 패키지로 사용되고 있다.

2. LGA (Land Grid Array, 표면실장 매트릭스 패드형 패키지)

- 패키지 밑면의 사각형 패드를 매트릭스로 나열한 형태이다.

- 패드형 특성상 BGA보다 훨씬 더 기생 인덕턴스가 적어 고속, 고주파 동작에 적합하고, 실장 높이를 줄일 수 있다.

- 현재 고성능 CPU의 패키지로 사용되고 있다. (i7 7700k CPU에 FCLGA1151 패키지가 적용되었다.)

(※ 볼의 높이가 0.1mm 이하의 BGA는 LGA로 분류된다 : JEITA규격)

접촉실장 패키지

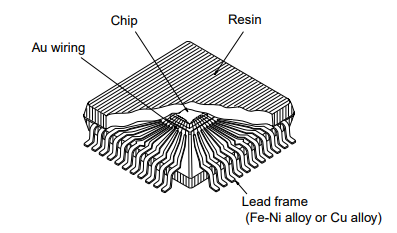

1. COF (Chip On Flexible Printed Circuit / Chip On Film)

- Bare Chip이 FPC(Flexible Printed Circuit)에 직접 실장되는 형태.

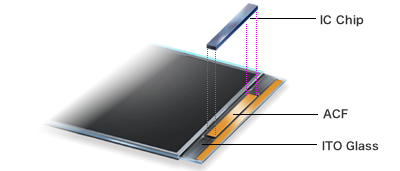

2. COG (Chip On Glass)

- (특히 LCD) 컨트롤러 Bare Chip이 유리위에 실장되는 형태.

3. COB (Chip On Board)

- PCB에 Bare Chip 고대로 본딩한 뒤, Molding하여 완전 밀폐하는 형태.

※ 1mil은 0.0254mm이다.

※ 주관적으로 조사할 필요없다 판단되는 패키지/파생패키지는 간략하게만 붙이거나, 제외하였다.

※ LCC, CLCC, PLCC 등의 Chip Carrier 관련 항목은 정의를 내리는데에 모호함이 느껴져 삭제하였다.

주요 참조

http://www.chip1stop.com/web/KOR/ko/tutorialContents.do?page=045

http://www.ti.com/lsds/ti_ko/quality/faqs/qfn_son_faqs.page

http://www.atsemi.com/sub.php?code=02_busi02&sel_type=6

https://www.fujitsu.com/cn/en/Images/contents2.pdf

https://blog.naver.com/rlaghlfh/110114451330

https://blog.naver.com/eztcpcom/220402216019

http://www.samsungsemiconstory.com/738

http://shannonstrutz.com/component-packages

http://www.cpushack.com/Packages.html

원글 출처:

https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=bae3421_&logNo=221260053942

'아트웍 > PADS' 카테고리의 다른 글

| PADS 명령어 (0) | 2023.05.04 |

|---|---|

| SMD2012 규격 (0) | 2023.02.15 |